UVMとは

UVM(Universal Verification Methodology)は、ハードウェアの検証を効率化するためのフレームワークであり、IEEE 1800 SystemVerilogの一部として提供されています。

UVMのテストベンチ構造は、UVC(Universal Verification Component)と呼ばれる再利用可能なコンポーネントで構成されます。

Hello Worldからはじめる

uvmで「Hello World」を表示させます。

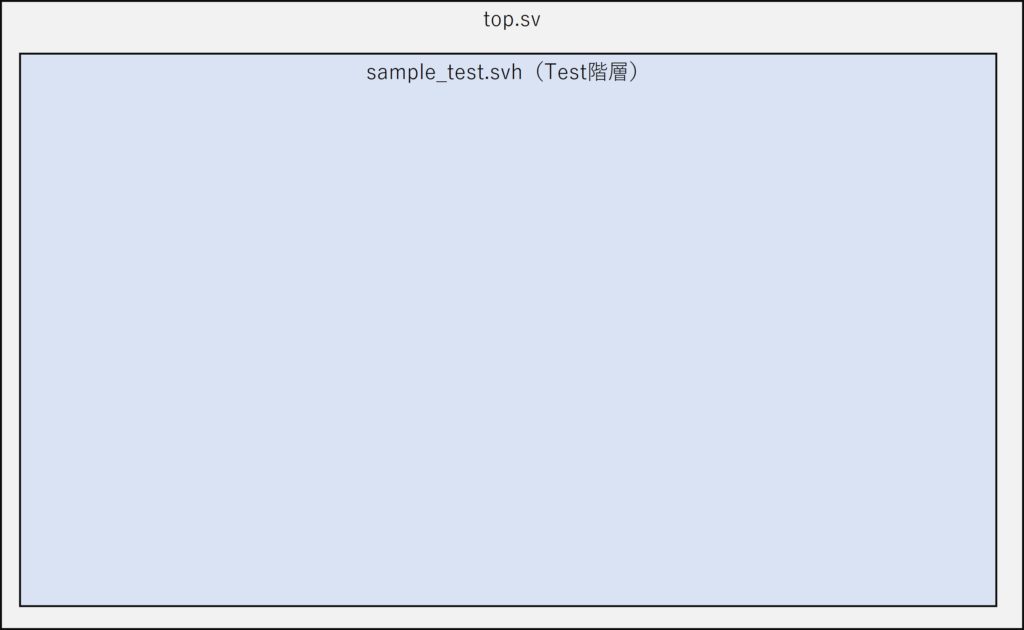

top.sv

module top;

`include "uvm_macros.svh" // uvmのマクロを有効にする。「`」で始まるやつ。

import uvm_pkg::*; // uvmのパッケージを有効にする。「`」以外。

class sample_test extends uvm_test; // 一番上はuvm_testを継承したclassを使用する。

`uvm_component_utils(sample_test) // sample_testをuvmのデータベースに登録する。

// systemverilogのクラスの構文。uvm独自ではない。

function new(string name="sample_test", uvm_component parent=null);

super.new(name, parent);

endfunction

// uvm独自の構文。

task run_phase(uvm_phase phase);

`uvm_info(this.get_name(), "Hello World", UVM_NONE);

endtask

endclass

initial begin

run_test("sample_test"); // `uvm_component_utils(<クラス>)で登録した<クラス>を実行する。

end

endmodule実行結果

[UVM_INFO][uvm_test_top] Hello World解説

uvmのマクロ、パッケージを使用する。

uvmはSystemVerilogで書かれているので、SystemVerilogの構文であるinclude, importでuvmを有効にします。

`include "uvm_macros.svh" // uvmのマクロを有効にする。「`」で始まるやつ。

import uvm_pkg::*; // uvmのパッケージを有効にする。「`」以外。uvm_testを継承したclassを作成する。

uvmでは最上位階層をuvm_testを継承したクラスから作成します。

class sample_test extends uvm_test; // 一番上はuvm_testを継承したclassを使用する。uvmデータベースにclassを登録する。

`uvm_component_utils(<クラス>)でuvmデータベースにclass名を登録します。

この操作で登録したclassをrun_test(“<クラス>”)で実行します。

`uvm_component_utils(sample_test) // sample_testをuvmのデータベースに登録する。 uvm_testの中身を書く。

function newはsystemveirlogのクラスの構文であり、uvmとは関係ないです。

task run_phaseはuvm独自でテストが実行されると呼ばれます。

// systemverilogのクラスの構文。uvm独自ではない。

function new(string name="sample_test", uvm_component parent=null);

super.new(name, parent);

endfunction

// uvm独自の構文。

task run_phase(uvm_phase phase);

`uvm_info(this.get_name(), "Hello World", UVM_NONE);

endtaskまとめ

uvmでHello Worldしました。

コメント