はじめに

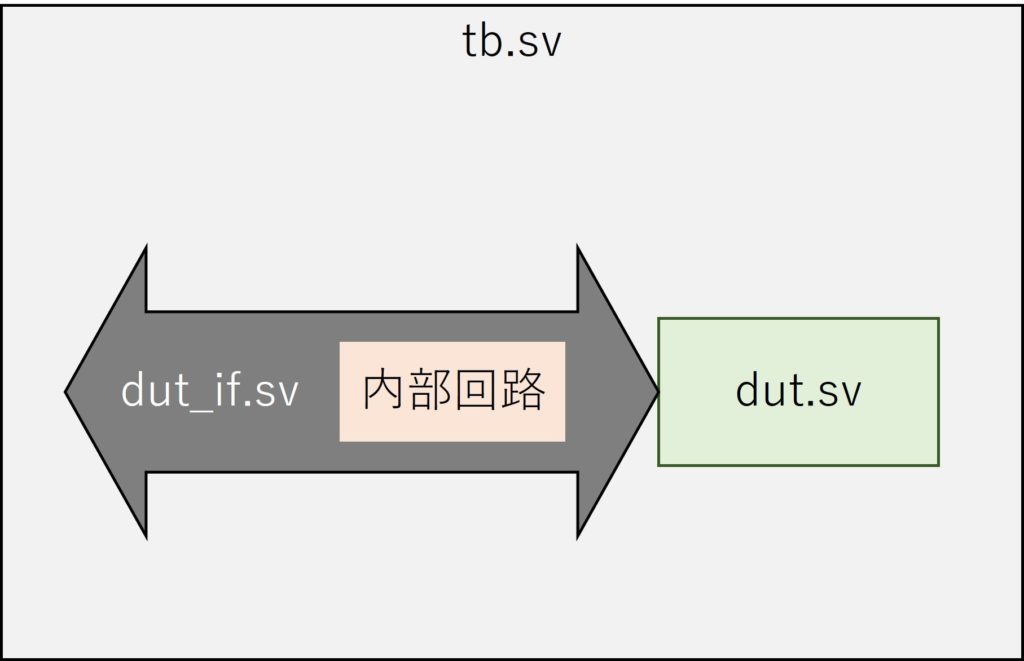

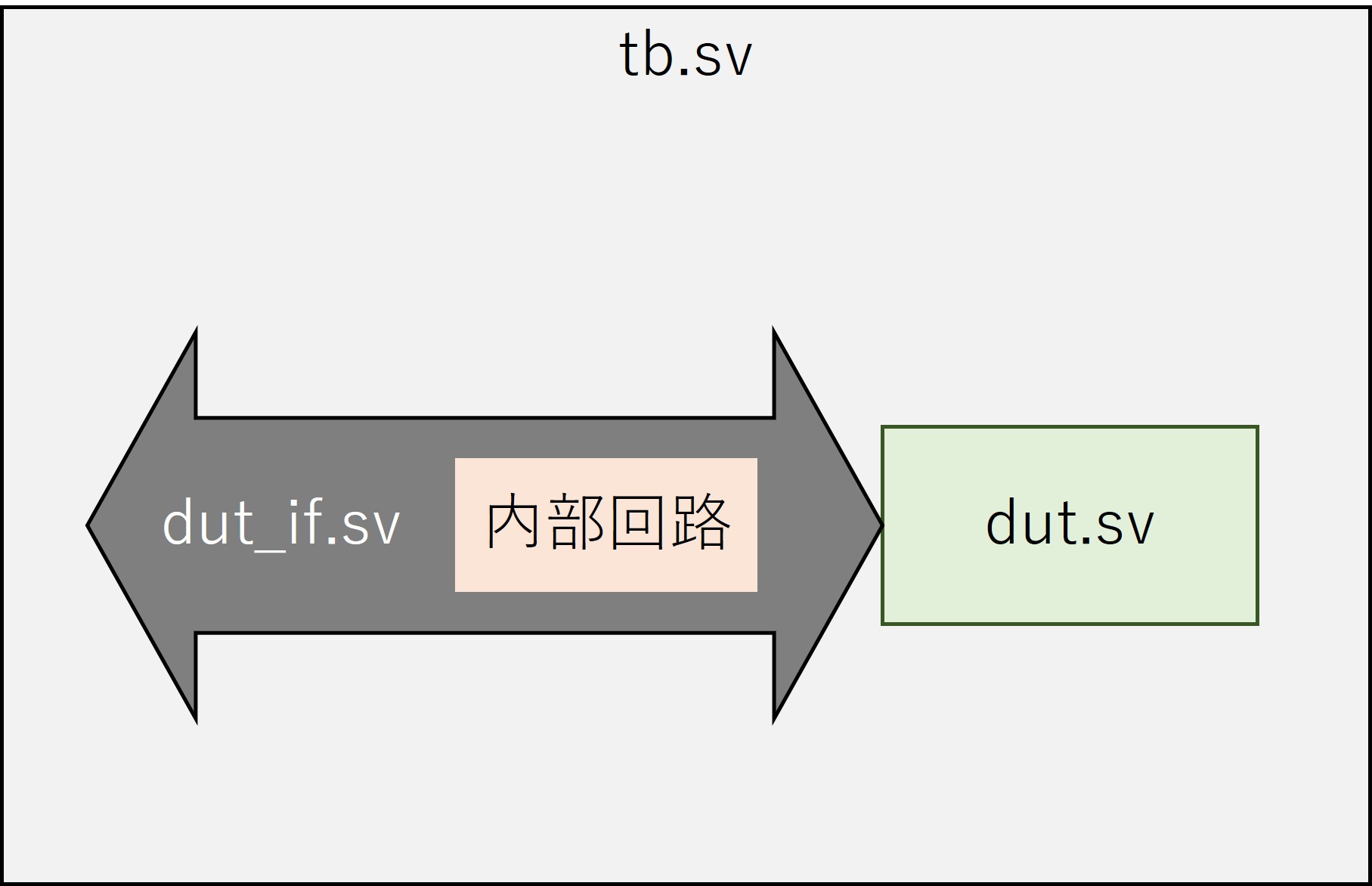

Interfaceブロックの中に回路を作成してみます。

サンプルコード

dut_if.sv

Interfaceです。validがHighのときのdinが有効データになります。

interface dut_if#(

parameter BW = 2

)(

input clk,

input rst_n,

input valid,

input [BW-1:0] din

);

logic [BW-1:0] dout;

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

dout <= '0;

end

else begin

if (valid) begin

dout <= din;

end

end

end

endinterfacedut.sv

dinを反転して出力します。

module dut#(

parameter BW = 2

)(

input clk,

input rst_n,

input [BW-1:0] din,

output logic [BW-1:0] dout

);

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

dout <= '0;

end

else begin

dout <= ~din;

end

end

endmoduletb.sv

module top;

bit clk = 0;

always #5 clk = ~clk; // クロック生成

bit rst_n = 0; // リセット生成

initial begin

#10 rst_n = 1;

#50;

$finish;

end

// dutのパラメータとか結線とか

localparam BW = 2;

bit valid = 1;

bit [BW-1:0] din;

bit [BW-1:0] dout;

always #10 din <= din + 1'b1; // 入力データ生成

// DUTの出力を表示

always @(posedge clk)

$display("%b", dout);

dut_if#(

.BW(BW)

) i_dut_if(

.clk(clk),

.rst_n(rst_n),

.valid(valid),

.din(din)

);

dut#(

.BW(BW)

) i_dut(

.clk(clk),

.rst_n(rst_n),

.din(i_dut_if.dout),

.dout(dout)

);

endmodule出力

00

00

11

10

01

00まとめ

Interfaceブロックに回路を作成しました。

コメント