Systemverilog

Systemverilog 【SystemVerilog】Constrained Randomについて考える

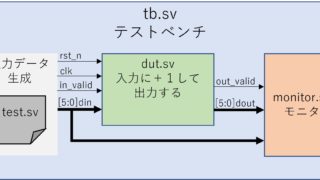

田中太郎Constrained Randomの考えを使った検証環境のサンプルを作成しました。本当はclassにrandの変数を定義してconstraintで範囲を決定→randomize()するのですが、constraintとrandomi...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog