田中太郎

画像データを二値化するSystemVerilogのサンプルコードです

サンプルコード

仕様

・ビット幅を変更可能

・閾値を変更可能

・閾値以下だとALL 0、閾値を超えるとALL 1を返す

・サイクル数:1

RTL

module binary #(

parameter BIT_WIDTH = 3,

parameter THRESHOLD = 3'011

)(

input clk,

input rst_n,

input [BIT_WIDTH-1:0] din,

output logic [BIT_WIDTH-1:0] dout

);

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

dout <= '0;

end

else begin

if (din > THRESHOLD) begin

dout <= '1;

end

else begin

dout <= '0;

end

end

end

endmoduleTestBench

module tb;

initial begin

$dumpfile("wave.vcd");

$dumpvars(0,tb);

end

initial begin

#100;

$finish;

end

reg clk = 0;

logic rst_n;

always #5 clk = !clk;

initial begin

rst_n = 0;

din = 0;

#10;

rst_n = 1;

end

always_ff @(negedge clk) begin

din += 1;

end

logic [2:0] din;

logic [2:0] dout;

binary #(

) dut(

.clk(clk),

.rst_n(rst_n),

.din(din),

.dout(dout)

);

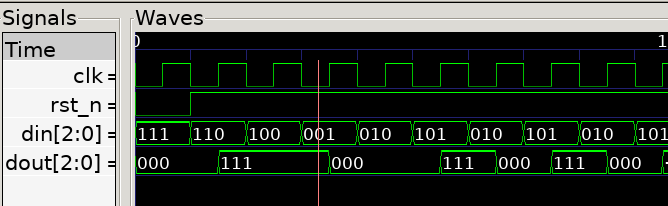

endmodule波形

まとめ

画像データを二値化するSystemVerilogのサンプルコードを紹介しました

コメント