functionでautomaticで宣言したときとstaticで宣言したときの違いを解説します

functionの使い方を知らない方はこちらから

automatic/staticとは

automatic/staticはfunction内で使用される変数を共有するかどうかを指定します

これだけではわからないと思うので、サンプルと伴に説明します

まず、automatic/staticをどのように使用するか説明します

automatic/staticの使い方

automatic/staticは以下のように使用します

function automatic func1(

input in1,

input in2

);

// なんらかの処理

endfunction

function static func2(

input in1,

input in2

);

// なんらかの処理

endfunctionautomatic/staticが指定されていないときはstaticと認識されます

では、両者にどのような違いがあるか見てみましょう

automatic/staticの動作の違い

サンプルコードを作成して両者の違いを見ていきます

サンプルコード

module top (

output logic dout_static1,

output logic dout_static2,

output logic dout_automatic1,

output logic dout_automatic2

);

function automatic func_automatic(

input en

);

logic tmp;

if (en) begin

tmp = 1'b1;

end

func_automatic = tmp;

endfunction

function static func_static(

input en

);

logic tmp;

if (en) begin

tmp = 1'b1;

end

func_static = tmp;

endfunction

assign dout_static1 = func_static(1'b1);

assign dout_static2 = func_static(1'b0);

assign dout_automatic1 = func_automatic(1'b1);

assign dout_automatic2 = func_automatic(1'b0);

endmodule入力が1なら1を出力し、入力が0なら不定(x)を出力するfunctionを

automaticとstaticでそれぞれ定義しました

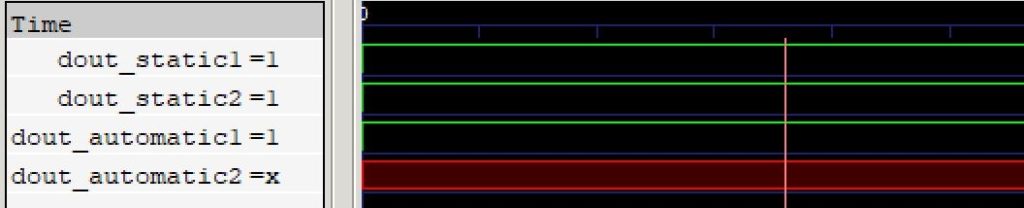

波形

automaticで定義したfunc_automaticは1を入力したら1を出力、0を入力したらxを出力しています

staticで定義したfunc_staticは1を入力したら1を出力、0を入力したら1を出力しています

なぜ、両者で出力に違いがあるのでしょうか?

まず、automaticで定義したときの例です

func_automatic(1’b1)の場合はif文の条件にあたって、tmpには1が代入されます

func_automatic(1’b0)の場合はif文の条件にあたらず、tmpには不定が代入されます

次に、staticで定義したときの例です

func_static(1’b1)の場合はif文の条件にあたって、tmpには1が代入されます

func_static(1’b0)の場合はif文の条件にあたりません

しかし、staticで定義するとfunc_static(1’b1)でtmpに代入した1が残っており

1が出力されます

まとめ

functionのautomaticとstaticの違いについて解説しました

コメント