オープンソースソフトウェア(OSS)を使ってlinux上にverilogの開発環境(コンパイル/シミュレーション)を作成します

はじめに

HDL(ハードウェア言語)を自宅で学習するためオープンソースで開発環境を整備しました

コンパイラ/シミュレータにIcarusVerilog、波形ViewerにGTKWaveというものを使います

IcarusVerilogはコンパイルからシミュレータ、論理合成までを行えますが

波形を表示するGUIを持たないのでGTKWaveを使って波形を表示します

環境

OS:CentOS 7

必要なソフトをインストールする

IcarusVerilogをインストールする

以下、事前に必要なソフトです

・autoconf

・gperf

・git

それぞれインストールしましょう。

CentOSでは「yum」を使ってインストールできます

sudo yum install autoconf

sudo yum install gperf

sudo yum install gitでは、実際にIcarusVerilogをインストールしましょう

まず、gitから必要ファイルを取得します

git clone https://github.com/steveicarus/iverilog.gitiverilogというディレクトリができているので、移動します

cd iverilogautoconf.shというファイルがあるので実行します

sh autoconf.shconfigureというファイルができるので、下記を順番に実行します

./configure

make

sudo make install以上でインストールが完了します。

GTKWaveをインストールする

GTKWaveに必要なファイルをダウンロードします

注)2020/12/27現在でgtkwaveのバージョンが3.3.107でした。

バージョンが変わった場合はファイル名が変わると思うので、公式サイトで確認してみてください。

wget http://gtkwave.sourceforge.net/gtkwave-3.3.107.tar.gz取得したファイルを解凍します

tar -zxvf gtkwave-3.3.107.tar.gzgtkwave-3.3.107というディレクトリができるので移動します

cd gtkwave-3.3.107あとは以下を順番に実行することでインストールできます

./configure

make

sudo make install以上でインストールが完了します

作成した環境の動作確認をする

IcarusVerilogとGTKWaveをインストールできたので、実際に動かしてみましょう

適当なRTLを作成します

counter.v

module counter(out, clk, reset);

parameter WIDTH = 8;

output [WIDTH-1 : 0] out;

input clk, reset;

reg [WIDTH-1 : 0] out;

wire clk, reset;

always @(posedge clk)

out <= out + 1;

always @reset

if (reset)

assign out = 0;

else

deassign out;

endmodule // counter次にテストベンチを作成します

テストベンチには$dumpfile(“<vcdファイル名>”)と$dumpvars(0, <テストベンチ名>)を記述する必要があります

test.v

module test;

/* Make a reset that pulses once. */

reg reset = 0;

initial begin

$dumpfile("test.vcd");

$dumpvars(0,test);

# 17 reset = 1;

# 11 reset = 0;

# 29 reset = 1;

# 5 reset =0;

# 513 $finish;

end

/* Make a regular pulsing clock. */

reg clk = 0;

always #1 clk = !clk;

wire [7:0] value;

counter c1 (value, clk, reset);

initial

$monitor("At time %t, value = %h (%0d)",

$time, value, value);

endmodule // testcounter.vとtest.vをIcarusVerilogを用いてコンパイルします

iverilog sample.v test.vコンパイルが成功するとa.outという名前のファイルが作成されています

IcarusVerilogでシミュレーションを実行します

vvp a.outシミュレーションが完了するとtest.vcdという波形ファイルが作成されます

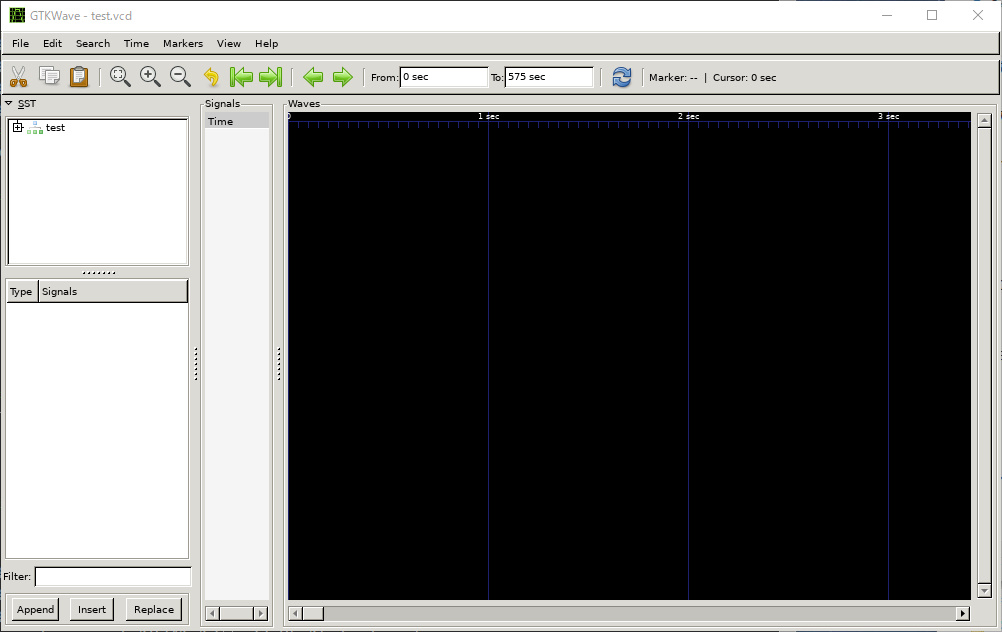

これをGTKWaveを用いてGUIで波形を表示させます

gtkwave test.vcd &GUIが起動すれば成功です

まとめ

今回はlinux環境にOSSを使ってVerilogの環境を作成しました

IcarusVerilog,GTKWaveの詳しい使い方はまたの機会に解説したいと思います

コメント