田中太郎

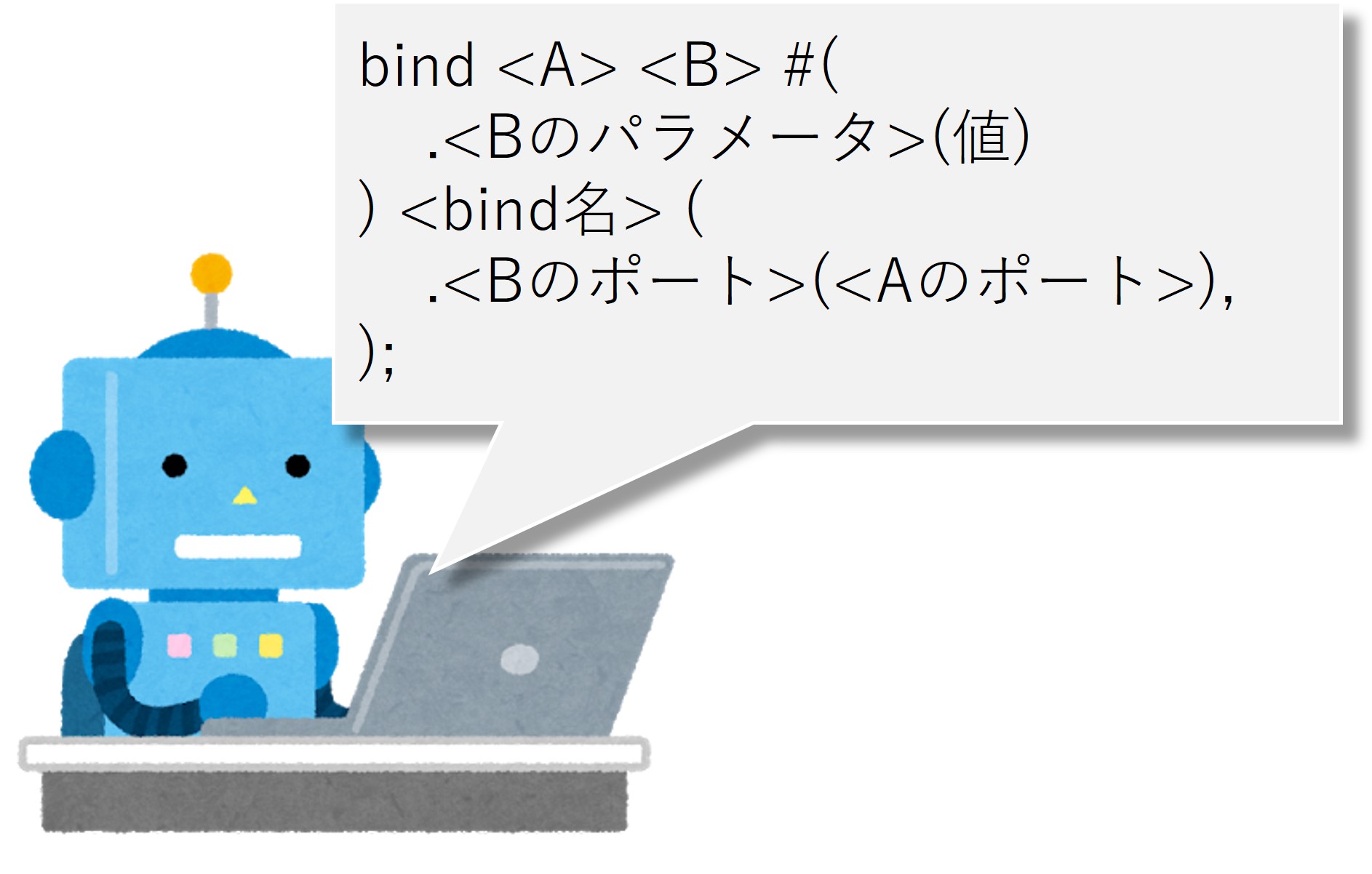

bindのparameterを使用します

使い方

bind <A> <B> #(

.<Bのパラメータ>(値)

) <bind名> (

.<Bのポート>(<Aのポート>),

);サンプルコード

以下のコードは、リセット解除されるとオール1を出力するDUTと

それを出力するモニタ

テストベンチから構成されています

module tb;

bit clk = 0;

bit rst_n = 0;

always #5 clk = !clk; // クロック生成

initial begin // テストシーケンス。リセットを解除するだけ

#10;

rst_n = 1;

#20;

$finish;

end

// dutをインスタンス

logic [2:0] dout;

dut u_dut(

.clk(clk),

.rst_n(rst_n),

.dout(dout)

);

// dutとモニタをbind

bind dut monitor #(

.BW(3)

) i_monitor(

.clk(clk),

.rst_n(rst_n),

.din(dout)

);

endmodule

// dut. リセット解除されるとAll 1が出力される

module dut #(

)(

input clk,

input rst_n,

output logic [2:0] dout

);

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

dout <= '0;

end

else begin

dout <= '1;

end

end

endmodule

// モニタ。リセット解除時のdinを表示する。

module monitor #(

parameter BW = 1 // テストベンチで3に上書きしています

)(

input clk,

input rst_n,

input [BW-1:0] din

);

initial begin

forever begin

@(posedge clk iff rst_n);

$display("%d", din);

end

end

endmodule出力

0

7

コメント