田中太郎

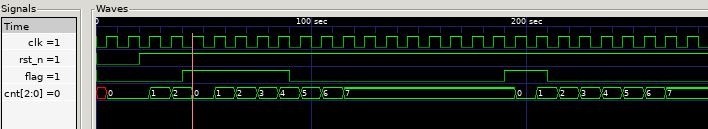

信号が最初に変化したときに初期値に戻るカウンタのサンプルコードです

サンプルコード

sample.sv

1クロックで1カウントアップします

最大値でホールドします

flagが0 -> 1に変化するとカウンタが初期化されます

module sample(

input clk,

input rst_n,

input flag,

output logic [2:0] cnt

);

// flagをFFでたたく

logic flag_d1;

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

flag_d1 <= '0;

end

else begin

flag_d1 <= flag;

end

end

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

cnt <= '0;

end

else begin

if (!flag_d1 && flag) begin // flagが0->1に変化すると初期化される

cnt <= '0;

end

else begin

if (cnt != '1) begin // 最大値にでホールドする

cnt <= cnt + 1'b1;

end

end

end

end

endmoduletb.sv

module tb;

initial begin

$dumpfile("wave.vcd");

$dumpvars(0,tb);

end

bit clk = 0;

bit rst_n = 0;

always #5 clk = ~clk;

bit flag = 0;

initial begin

#20;

rst_n = 1;

#20;

flag = 1;

#50;

flag = 0;

#100;

flag = 1;

#20;

flag = 0;

#100;

$finish;

end

logic [2:0] cnt;

sample #(

) u_sample(

.clk(clk),

.rst_n(rst_n),

.flag(flag),

.cnt(cnt)

);

endmodule波形

まとめ

信号の変化点で初期化するカウンタを作成しました

コメント