Systemverilog

Systemverilog 【SystemVerilog】UVMで検証環境を作成する~Virtual InterfaceでクラスとDUTを接続する~【#5】

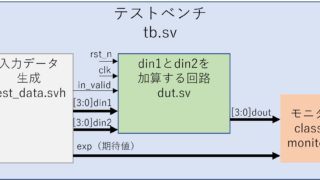

前回のおさらいSequence_item/Sequencer/Driver/Sequenceを作成してテストベンチに組み込みました。ここまではclass内で完結する話でした。Virtual InterfaceでclassとDUTを接続する今...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Python

Python  Python

Python  Python

Python