Systemverilog

Systemverilog 【SystemVerilog】interfaceを使用して回路を作成する

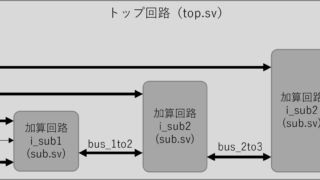

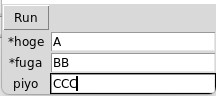

田中太郎 UVMの検証環境ではinterfaceをよく使用します RTLでも使用できるので、サンプルを作成しました 回路仕様 dinにオフセットを3回に分けて加算して出力します in_validが1のときのdinが有効データで、 out_v...

Systemverilog

Systemverilog  Python

Python  Python

Python  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog