田中太郎

SystemVerilogのPackageについて考えていきます

はじめに

packageで検証部品はひとまとめにすることで再利用性が上がります

サンプルコードを用いてpackageの使い方について解説します

サンプルコードと解説

pkg.sv

package pkg; // パッケージを定義

function void print();

$display("==========");

$display("base_test");

$display("==========");

endfunction

endpackagepackage <パッケージ名>;

・・・中身・・・

endpackage

でパッケージを作成できます

sample.sv

module sample;

import pkg::*; // pkgの中身を使用できるようにする

initial begin

print(); // pkgで定義されたprint()が使える

end

endmoduleimport <パッケージ>::*;

で<パッケージ>で定義したfunction/task/class/定数/を使えます

pkg.svでprint()を定義したので、4行目でprint()が使えるようになります

また、

pkg::print()

のようにすればimportしなくても、pkg.svで定義したものを使用できます

実行結果

==========

base_test

==========使う場面

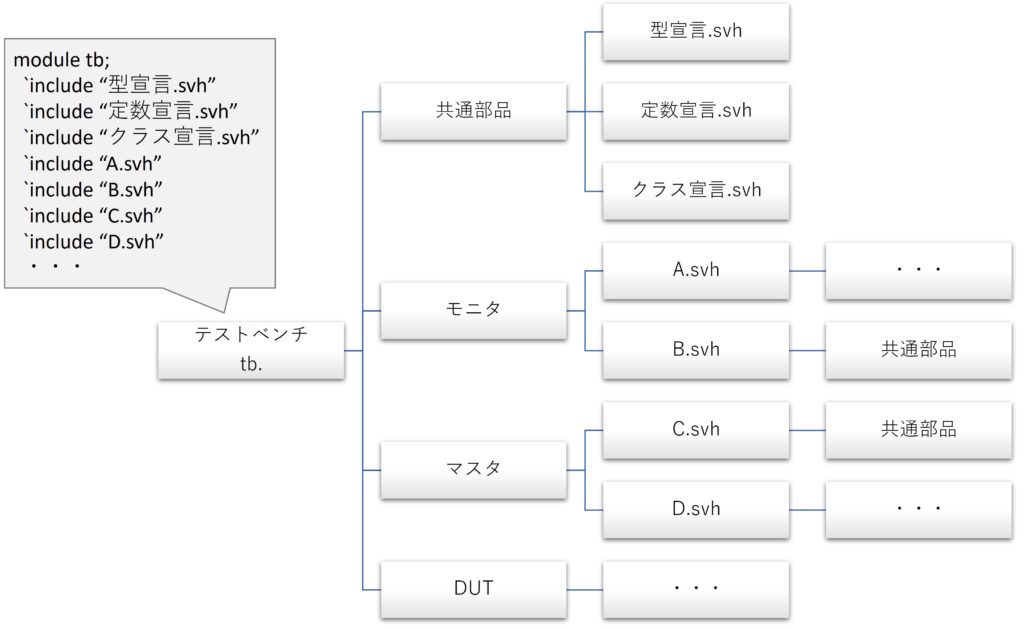

例えば以下のような構成のテストベンチがるとしましょう

テストベンチではモデル・モニタが増えるたび必要なsvhファイルをインクルードする必要があります

モデル・モニタの階層が深くなるにつれ、インクルードするファイルが多くなり管理が大変になります

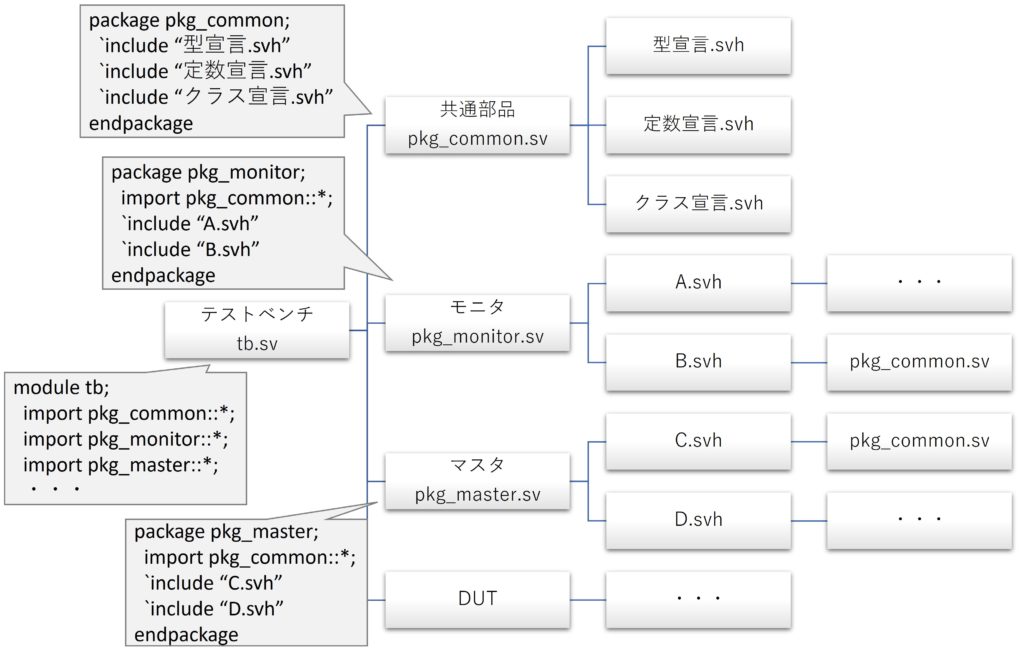

そこで、packageを使って「ひとまとめ」にします

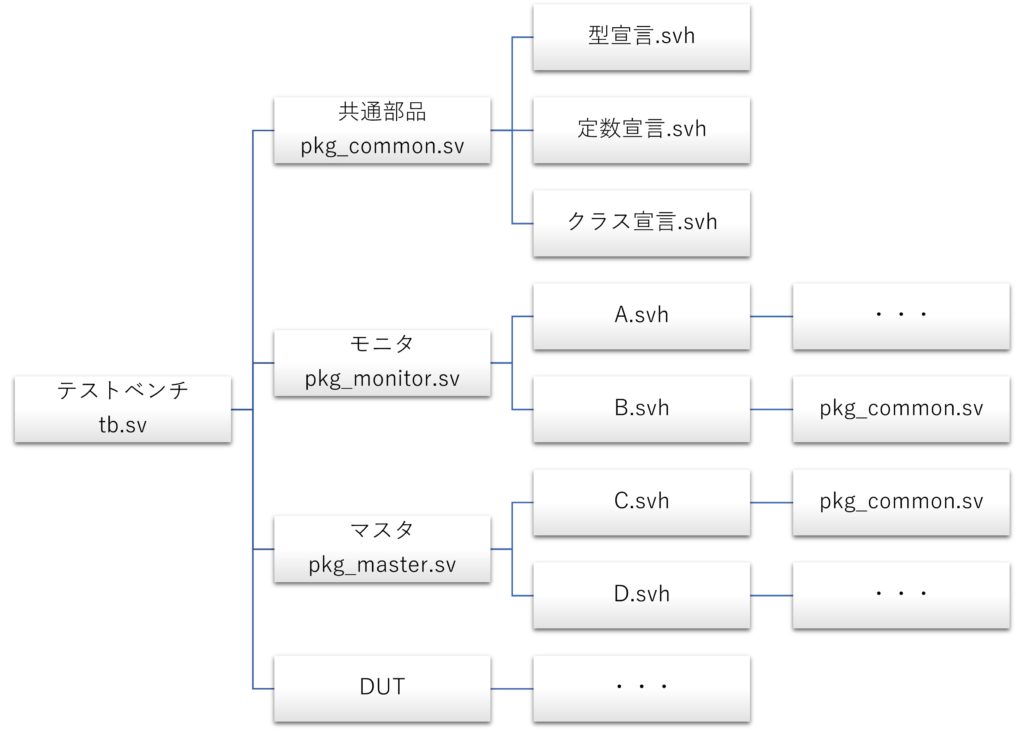

共通部品をpkg_common.sv, モニタをpkg_monitor.sv, マスタをpkg_master.svで

パッケージ化します

パッケージ化することで、テストベンチはimportしたパッケージ以下の構成を意識しなくてよくなります

まとめ

packageの使い方について解説しました

再利用性が上がるので積極的に使用していきましょう

コメント