田中太郎

3ビットカウンタを作成します

仕様

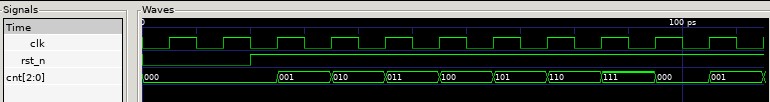

リセットで初期化して1クロックごとに1カウントアップします

サンプルコード

サンプルコードです

sample.sv

module sample #(

parameter BW = 3

)(

input clk,

input rst_n,

output logic [BW-1:0] cnt

);

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin // リセットが0で初期化

cnt <= '0;

end

else begin // クロックの立ち上がりで+1

cnt <= cnt + 1'b1;

end

end

endmodule動作確認する

テストベンチを作成して動作確認します

tb.sv

module tb;

initial begin // 波形を取得します

$dumpfile("wave.vcd");

$dumpvars(0, tb);

end

bit clk = 0;

always #5 clk = ~clk; // クロックを生成します

bit rst_n = 0;

initial begin // リセットを解除します

#20;

rst_n = 1;

#100;

$finish;

end

logic [3:0] cnt;

sample #( // カウンタ回路をインスタンスします

) u_sample(

.clk(clk),

.rst_n(rst_n),

.cnt(cnt)

);

// リセットが1でクロックが立ち上がったときのカウンタ回路の出力を表示します

always_ff @(posedge clk iff rst_n) $display("%d", cnt);

endmodule出力

$displayで表示する標準出力です

0

1

2

3

4

5

6

7

0

1波形

まとめ

3ビットカウンタを作成しました

コメント