Systemverilog

Systemverilog Pullup/Pulldown 実機とシミュレーションの違い

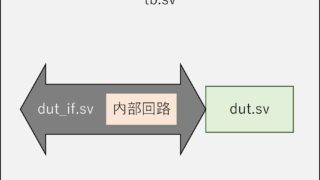

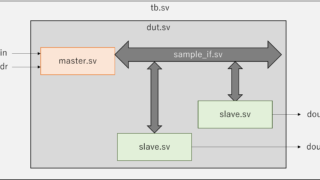

はじめにFPGA開発では基板上で信号がPullup/Pulldownされている信号があります。基板上でPullup/Pulldownされているということは、DUTには表現されません。シミュレーションでは注意が必要で、テストベンチ側でPull...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog