Systemverilog

Systemverilog 【SystemVerilog】UVMで検証環境を作成する~なるべく最小構成~【#8】

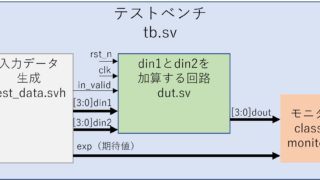

前回のおさらいVirtual SequenceとVirtual Sequencerを作成しました。今回は、これまで作成したテストベンチをなるべく短いコードで再掲します。なるべく最小構成top.sv(最上位階層)top.svmodule to...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog