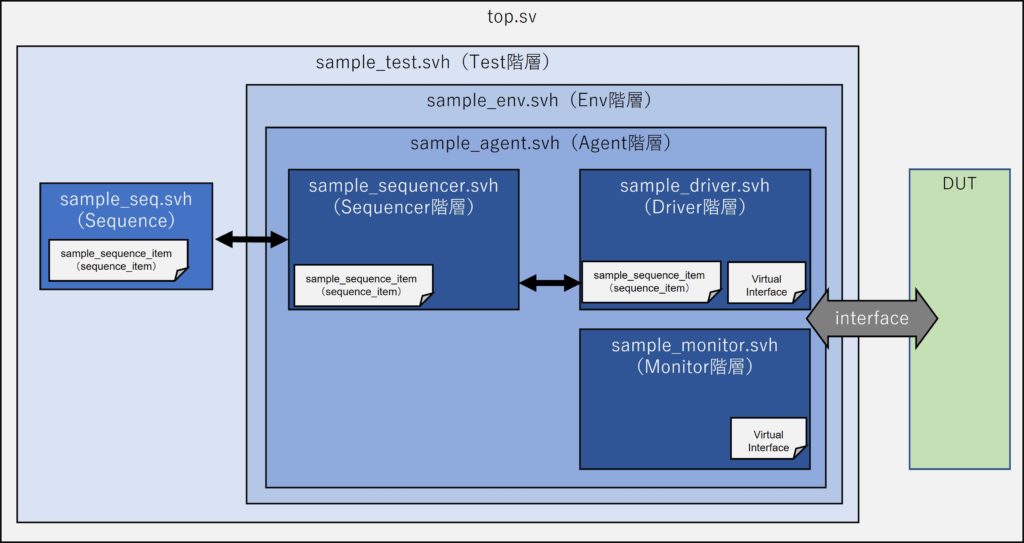

前回のおさらい

Virtual Interfaceを追加してDUTをテストベンチを接続しました。

Monitorを追加する

前回使用したVirtual Interfaceを使ってテストベンチにMonitor階層を追加します。

uvm_monitorを継承してsample_monitor.svhを作成します。

sample_monitor.svh

class sample_monitor extends uvm_monitor;

`uvm_component_utils(sample_monitor)

virtual sample_if vif;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

if (!uvm_config_db#(virtual sample_if)::get(this, "", "vif", vif))

`uvm_fatal(this.get_name(), "vif is invalid")

endfunction

task run_phase(uvm_phase phase);

int exp;

forever begin

#10;

exp = vif.din1 + vif.din2;

`uvm_info(this.get_name(),

$sformatf("exp %d, act %d", exp, vif.dout), UVM_LOW)

end

endtask

endclassMonitor階層をsample_agent.svhにインスタンスします。

sample_agent.svh(sample_monitor.svhをインスタンスする)

class sample_agent extends uvm_agent;

`uvm_component_utils(sample_agent)

sample_driver driver;

sample_sequencer sequencer;

sample_monitor monitor; // 追加。

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

driver = sample_driver::type_id::create("driver", this);

sequencer = sample_sequencer::type_id::create("sequencer", this);

monitor = sample_monitor::type_id::create("monitor", this); // 追加。

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

driver.seq_item_port.connect(sequencer.seq_item_export);

endfunction

task run_phase(uvm_phase phase);

`uvm_info(this.get_name(), "Agent", UVM_NONE)

endtask

endclass前回、Driverのデバッグ用に使用した記述を削除します。

top.sv(Driverのデバッグ用の記述を削除する)

module top;

`include "uvm_macros.svh"

import uvm_pkg::*;

`include "sample_sequence_item.svh"

`include "sample_monitor.svh" // 追加。

`include "sample_sequencer.svh"

`include "sample_driver.svh"

`include "sample_agent.svh"

`include "sample_env.svh"

`include "sample_seq.svh"

`include "sample_test.svh"

initial begin

run_test("sample_test");

end

sample_if vif();

initial begin

uvm_config_db #(virtual sample_if)::set(null, "*", "vif", vif);

end

bit [4:0] dout;

dut i_dut(

.din1(vif.din1),

.din2(vif.din2),

.dout(vif.dout)

);

// initial begin // Driverのデバッグ用なので削除します。

// #5;

// $display("din1 %d", vif.din1);

// $display("din2 %d", vif.din2);

// $display("din3 %d", vif.din3);

// $display("dout %d", dout);

// end

endmoduleその他のファイルはそのままです。

実行結果

[UVM_INFO][uvm_test_top] Hello World

[UVM_INFO][env] Env

[UVM_INFO][agent] Agent

[UVM_INFO][sequencer] Sequencer

[UVM_INFO][driver] Driver

[UVM_INFO][monitor] exp 11, act 11解説

Virtual Interfaceの接続方法はDriverと同じなので割愛します。

まとめ

Monitorを追加しました。

コメント