田中太郎

モニタを作成します

期待値は今回は省略して、値を標準出力するだけです

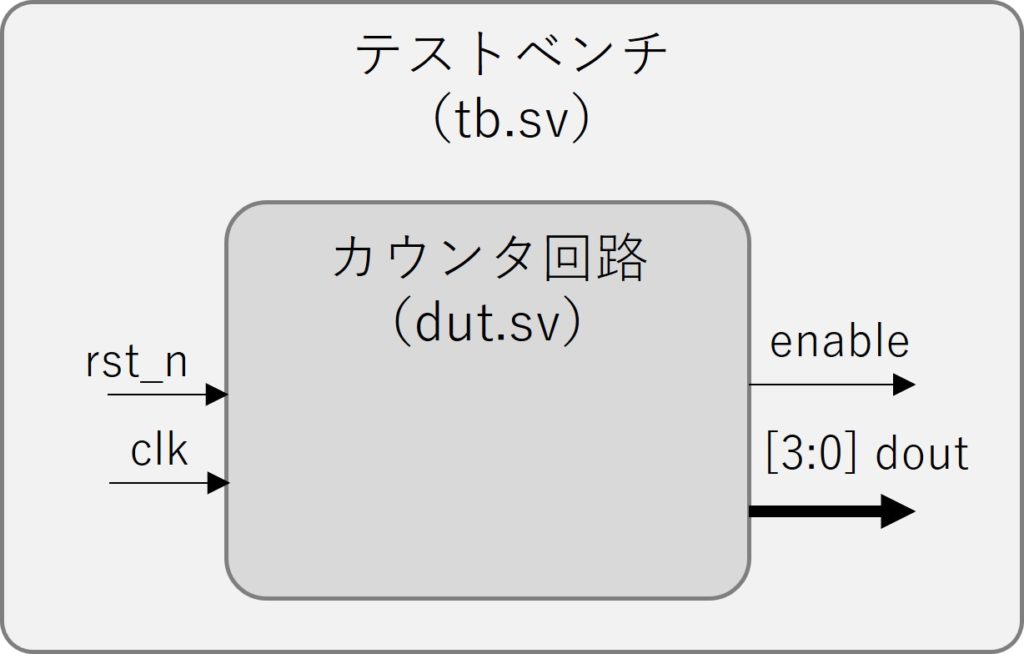

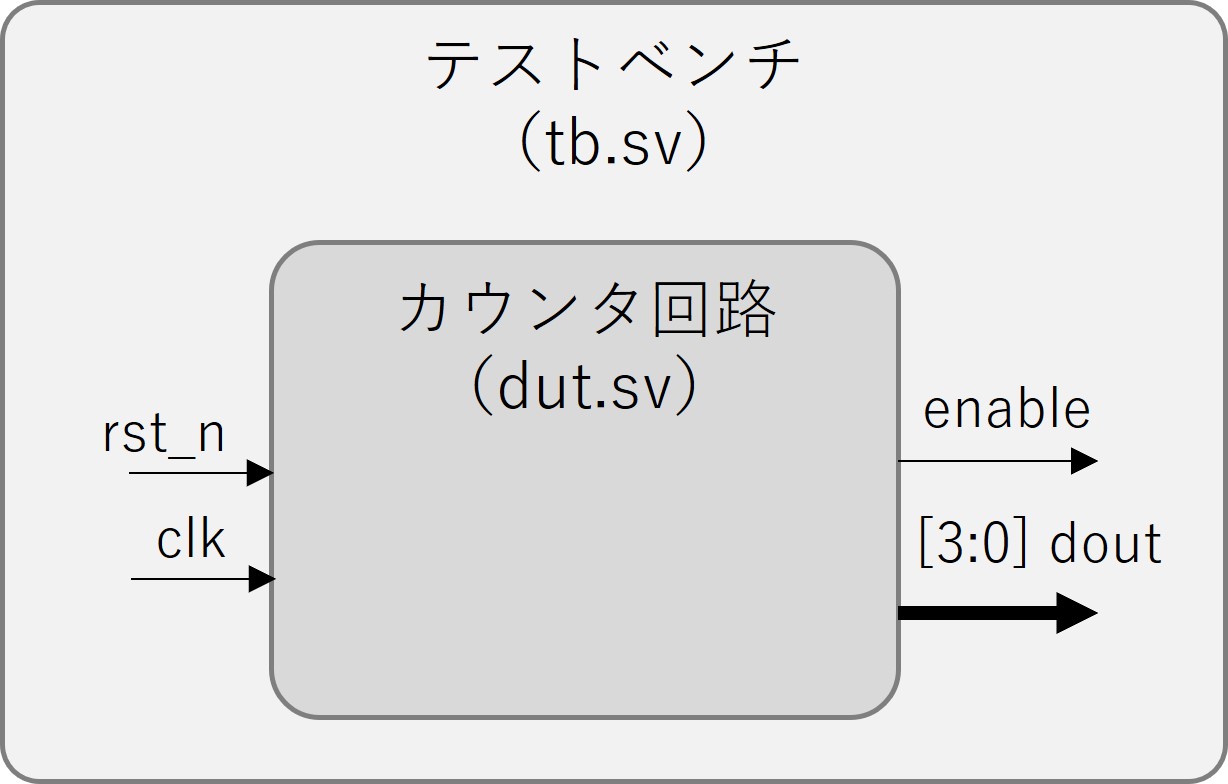

構成

DUTとテストベンチに分けて説明します

カウンタ回路

今回モニタする回路です

リセットで初期化(0)するカウンタ回路です

入力ポート

・clk:クロック

・rst_n:非同期リセット。1でカウンタ値が初期化される

出力ポート

・dout:カウンタ値を出力する

・enable:カウンタ値が奇数のとき、enableが1になる

dut.sv

module dut #(

)(

input clk,

input rst_n,

output logic enable,

output logic [3:0] dout

);

always_ff @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

dout <= '0;

end

else begin

dout <= dout + 1'b1;

end

end

assign enable = dout[0];

endmoduleテストベンチ

モニタを実装しています

説明はコード上に記載します

module tb;

bit clk = 0;

bit rst_n = 0;

always #5 clk = ~clk; // クロックを生成

bit enable;

bit [3:0] dout;

initial begin // シーケンス。モニタをONしてリセットを解除する

fork

monitor(); // fork/join_noneでモニタを生成。joinだと次の行に進まなくなるので、join_none

join_none

#20;

rst_n = 1;

#200;

$finish;

end

// モニタのタスク。

// foreverを使ってenableが1のときのdoutを表示する.

// 期待値があるときは、displayのところで比較すればよい。

task monitor;

$display("***Start Monitor***");

forever begin

if (enable) begin

$display("%d", dout);

end

@(posedge clk);

end

endtask

// dutをインスタンス

dut #(

) u_dut (

.clk(clk),

.rst_n(rst_n),

.enable(enable),

.dout(dout)

);

endmoduleまとめ

モニタを作成してDUTの出力をチェックしました

コメント