Systemverilog

Systemverilog UVM Virtual SequenceでSequenceを実行する方法まとめ

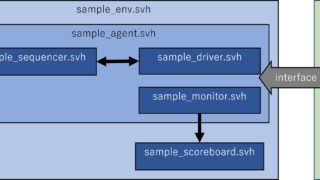

サンプルコードsample_seq.svh(Sequence)今回使用するSequenceです。クラス変数として、din1とdin2を持ちます。class sample_seq extends uvm_sequence #(sample_s...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog