Systemverilog

Systemverilog VerilogでJSONフォーマットを読み込む

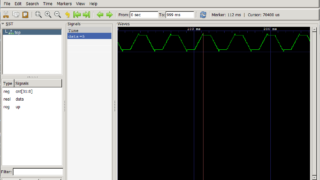

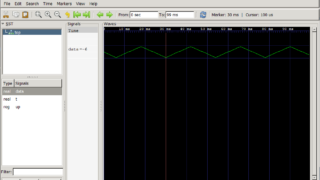

はじめに VerilogでJSONフォーマットを読み込みます。 JsonのパースにはJSON11を使用します。JSON11はC++なので、VPIでVerilogとデータのやり取りを行います。 サンプルコード まずはCコードを作成します。JS...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog