Systemverilog

Systemverilog SystemVerilog|パラレルシリアル変換回路

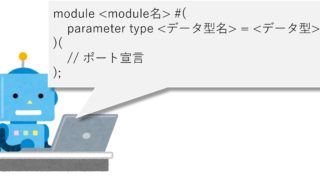

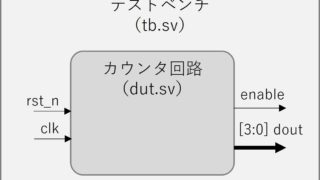

田中太郎 パラシリ変換回路を作ります サンプルコード initの立ち上がりで入力されたパラレルデータをシリアルデータに変換します sample.sv module sample #( parameter BW = 10 )( input c...

Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog  Systemverilog

Systemverilog